#### MODEL ADC-P

#### 16 CHANNEL HIGH SPEED SCANNING ADC

#### FEATURES:

- · 10USEC. CONVERSION TIME, 6USEC OPTIONAL

- 12 BIT RESOLUTION

- · SAMPLE AND HOLD INPUT AMPLIFIER

- 16 DIFFERENTIAL INPUTS

- · INTERNAL DATA MEMORY

- · CONTINUOUS AND SINGLE CYCLE SCANNING MODE

The Joerger Enterprises, Inc. Model ADC-P is a 16 channel scanning ADC packaged in a single width CAMAC module. It can accept up to 16 differential inputs and scan them continuously, or under program control be switched to a single scan mode. To improve accuracy, the input uses a sample and hold amplifier which holds the analog signal during conversion. A complete conversion cycle takes 10usec. per channel with a 6usec. version available. Three input ranges are available; +10.24, +5.12, or 0 to +10.24 volts. These ranges are switch selectable. Bipolar data is in 2's compliment and justified to 16 bits. Identity words are provided that read out the type of module, the input range selected and whether the module is in continuous or single scan mode. The module enters the single scan mode on command, resets itself to channel zero and scans all 16 channels. When in single scan the module can also accept an external, optically isolated trigger that will set the module to zero and cycle through all 16 channels. The converted data is stored in a 16 word data memory. The use of an internal data memory greatly simplifies system operation. The module operates as a complete analog input block, converting data and storing it in memory for readout. Internal logic insures that dataway read cycles and module write cycles never interfere. The analog section is powered by tracking 15 volt regulators to improve performance.

# SPECIFICATIONS

#### ANALOG INPUTS

Channels 16 differential inputs

Ranges  $\pm 10.24$ ,  $\pm 5.12$ , 0 to  $\pm 10.24$ v internally

switch selectable (shipped 0 to +10.24v).

Resolution 12 Bits

Input Protection +35 volts crate power on, +20 volts crate

power off.

Input Impedance 1M ohms

Conversion Time 10usec. per channel, 6usec. optional

Common Mode Rejection 50db minimum from D.C. to 1KHZ.

Absolute Accuracy at 25°C +.03% of F.S., + LSB maximum

Nonlinearity +⅓ LSB maximum

Temperature Coefficient of Gain +50ppm/OC maximum

"NEW"

## CAMAC COMMANDS

$N \cdot F0 \cdot A_{0-15}$  Reads out data from selected channel onto R

lines 1-12, bipolar outputs have sign extension

to bit 16.

N·Fl·Al5 Reads out the module-type, the input range and

operating mode, continuous or single cycle,

and if module is active.

N·F6·A0 Reads out module type (R7, R9) N·F24·A0 Sets module into continuous scan mode.

N·F26·A0 Sets module into single scan mode, resets channel

address and performs a complete scan of all 16

channels.

(Z+C)S2 AND POWER UP Initializes module and places in continuous scan

mode.

X RESPONSE An X response is generated for all valid commands.

Q RESPONSE A Q response is generated for FO and F1-A15.

SINGLE SCAN TRIGGER An optically isolated input that will reset the address

counter and scan all 16 channels if in the single scan

mode.

VISUAL INDICATORS

"N" Module is addressed.

Active Module is scanning.

Single Scan Module is in single scan mode.

POWER +24v, +6v, 8 watts maximum

SIZE Single width CAMAC module.

INPUT CONNECTOR Inputs are on rear printed circuit board. Compatible

with Viking 3V18 connector. Front panel connector

optional.

TEMPERATURE RANGE 0°C to 50°C

JEI0582

#### MODEL ADC-P

## 16 CHANNEL HIGH SPEED SCANNING ADC

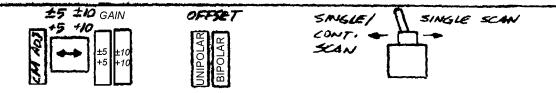

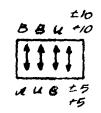

The Joerger Enterprises, Inc. Model ADC-P is a 16 channel scanning 12 bit ADC with an internal data memory. It has a cycle time of less than 160 usec corresponding to a per channel conversion of better than 10 usec. To improve accuracy a high speed sample and hold amplifier is incorporated. The module accepts up to 16 differential inputs, scans tham and switches them into a common This amplifier is a high input impedance operational amplifier configured with a gain of approximately one. This takes the differential input and converts it to a single ended signal. The output of this amplifier then goes to another amplifier which is used in gain selection. It has two gain settings with a gain of one or two. These are switch selectable with the gain of one being used for ranges +10V and +10V, and the gain of two for ranges +5V The output of this amplifier feeds a 1 usec sample and hold amplifier which stores the analog signal during conversion. output of the amplifier goes to a high speed ADC through a range selection switch. Input ranges provided are +10.24, +5.12, +10.24 and +5.12 volts. Nine switches are used to select the range. switches set the analog input into the ADC itself and in addition they select bipolar or unipolar mode, 2's compliment or straight binary output, and range information for readout by F1.Al5 to identify the range selected. All nine switches must be set for the module to operate correctly.

The module has two modes of operation, continuous and single cycle. The operating mode can be set under program command or with an on board toggle switch. The unit is controlled by a four bit counter. The standard unit contains a 6 usec ADC and a 1 usec sample and hold and thus can operate easily at the 10 usec scan time used. However, to improve accuracy as much as possible, the multiplexer and memory address are handled separately. When the sample and hold amplifier switches to hold, the ADC is triggered and the multiplexer is switched to the next channel while the memory address remains at the present address for the converted data to be loaded. This then allows the multiplexer, input amplifier and the amplifier in the sample and hold to acquire the new channel while the ADC is converting the last channels information which is stored in the sample and hold. addressing scheme is accomplished by using an adder in addition to the main address counter. The address counter controls the memories while the output of the adder which has added a one to the address counter controls the multiplexer keeping it one channel ahead.

The data memory is a 16x16 high speed Schottky memory. This internal memory greatly simplifies the use of the module. In continuous mode the module continuously scans the 16 channels and loads the data into memory. When data from one of the channels is required that channel can individually be addressed and the last converted data will be read out. The only disadvantage is that the data may be up to 15 channels (150 usec) old. Because the module must be able to read

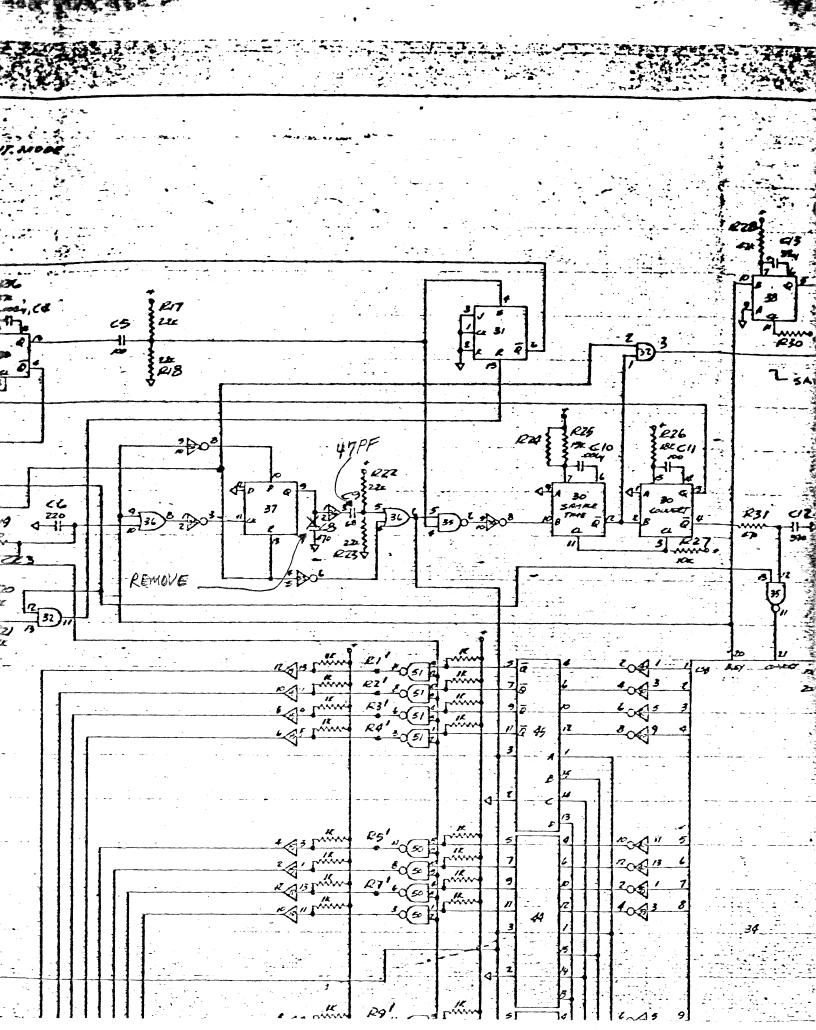

out or write into the memory care is taken to insure these cycles do not interfere. This is accomplished by the use of high speed memories and the fact that when a module is commanded to read out, the actual data is recorded by the controller at S1. This is at least 400 nsec after the command is initiated. A portion of this time, 200 nsec, is used by the module to decide when to write into memory. Upon receipt of a read command the module internally delays this signal by 200 nsec before gating out the data. Now if at the end of a conversion there is no read signal present, the module updates the memories which takes 100 nsec. If a read signal is present, the memories are not updated until the read signal is removed. In this way the read and write cycles never appear to the outside world to interfere.

In addition to the continuous scan mode a single scan mode is provided. Command F26 or the on board switch places the unit in single scan. In response to command F26 the module resets the address counter and scans all 16 channels and stops. When the module is in a single scan it can also be triggered externally. An optically isolated input is provided that will also reset the address counter and scan the 16 channels. Function F24, a reset, or the on board switch will place the unit into continuous scan mode.

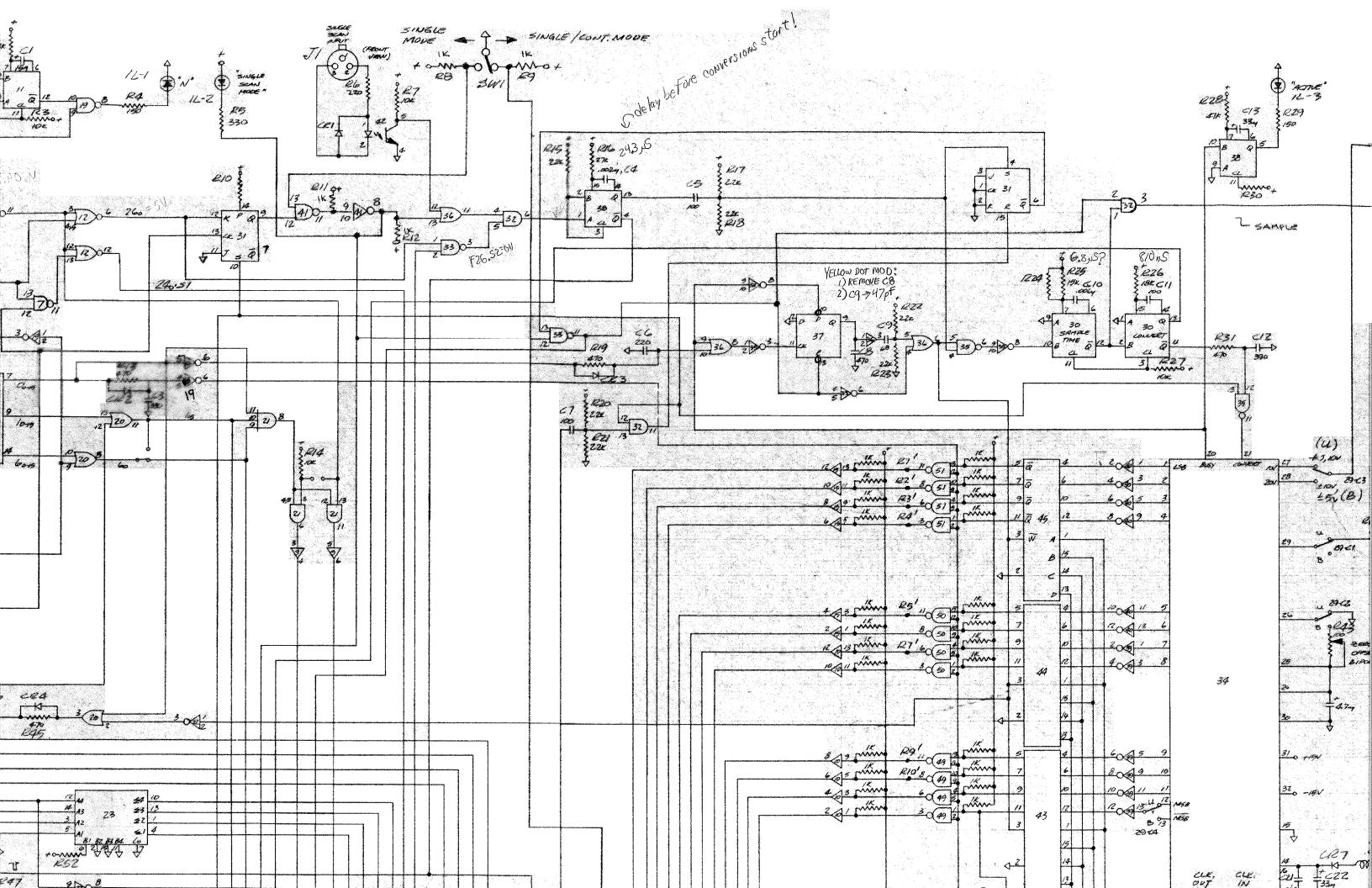

## CIRCUIT DESCRIPTION

The commands used in the Model ADC-P are F0·A0-A15, F1·A15, F6·A0, F24·A0 and F26·A0. Commands F24 and F26 are fully decoded by IC's 5, 6, 7, 8, 12, and 19. These commands are used to trigger the continuous/single flip-flop, IC 31. To decode F0, F1 and F6, IC's 6, 13, 8, 14, and 20 are used. Command F0 with the appropriate subaddress is used to read out data. F1·A15 reads out the status of the module as follows:

| R1<br>R2 | MODE<br>ACTIVE | "l"= Single Scan, "0"= Continuous Scan "l"= Module Active, "0"= Module Inactive |          |           |            |          |     |

|----------|----------------|---------------------------------------------------------------------------------|----------|-----------|------------|----------|-----|

|          |                | +10.24v                                                                         | +5.12v   | +10.24v   | +5.12v     |          |     |

| R3       | RANGE          | _ 0                                                                             | 1        | 0         | 1          |          |     |

| R4       | RANGE          | 0                                                                               | 0        | 1         | 1          |          |     |

| R5       | READS ON BOARD |                                                                                 |          |           |            |          |     |

|          | SWITCH         | "1"= Sin                                                                        | gle Scan | , "0"= Co | ontinuous/ | Single M | ode |

F6.A0 is used to read out the module identity, which is a "1" on R7 and R9. All commands return both an X and Q response.

The modules address is controlled by a four bit counter, IC25; an adder, IC 23; and a data selector, IC 24. The counter itself controls the memory address. The selector is used to switch the memory address during a data read to the dataway address lines. The adder is used to control the multiplexer address keeping it one channel ahead. When the module is reset either by (Z+C)S2 or when going into single scan the counter is reset to 15 thus placing the multiplexer on Channel 0.

The ADC Busy signal controls the module cycling. The busy signal is gated with the read signal in IC 36 to determine whether the modules memories can be updated at the end of busy. If there is no read signal, the trailing edge if busy will clock flip-flop 37, if there is a read signal present when it goes away it will clock IC 37. The output of this flip-flop is differentiated and loads the memory and triggers the sample mono. This places the sample and hold amplifier in sample for approximately 3 usec to acquire the next channels analog data. At the end of this time the module is placed in the hold mode, the counter is updated and a convert command is sent to the ADC.

In the single scan mode the timing is similar. However, upon receipt of F26 or the external single scan signal the module is first reset by mono IC 38. A short time later flip-flop 31 is set and a trigger is generated to take the first sample. This proceeds as in the continuous mode until channel 16 is complete. At this time IC 37 is clocked causing IC 31 to be reset stopping the scanner.

### CALIBRATION

Whenever the input range is changed the modules calibration should be checked. There are two adjustments to be made, they are gain and offset. There are two offset adjustments, one used for bipolar inputs and one for unipolar inputs. For bipolar ranges either +10.24v or +5.12v the bipolar adjustment is made with the lowest input level +3 LSB. For +10.24v this would be an input voltage of -10.2375v. With this input the pot should be adjusted to read between all zeros on bits 1-11 and all zeros and a "1" in the LSB. Note, bit 12 reads "1" for negative inputs and because of sign extension a "1" will also be on bits 13-16. Next the gain should be adjusted. This is done by putting in the highest level input minus 1½ LSB. For +10.24v range this would be +10.2325v. With this input the gain pot should be set to read between all "l"'s on bits 1-11 and all "l"; s and a zero on the For the unipolar input of +10.24v the unipolar offset should be set with an input of +.00125v and the gain set at +10.23625. For the +5.12v range the unipolar offset should be set with an input of +.000625v and the gain set with an input of +5.118125v.

MODEL ADC-P

# INPUT CONNECTOR

36 PIN P.C. EDGE CONNECTOR

MATING HALF - VIKING 3V18

# (VIEWED FROM REAR OF MODULE)

| Solder Side |    | PIN #  | PIN # | Compo       | nent   | Side |        |

|-------------|----|--------|-------|-------------|--------|------|--------|

| CHANNEL     | 0  | RETURN | 1A    | <b>1</b> B  | CHANNE | r o  | SIGNAL |

| "           | 1  | **     | 2 A   | <b>2</b> B  | ***    | 1    | ***    |

| 11          | 2  | "      | 3A    | 3B          | 11     | 2    | 11     |

| II          | 3  | "      | 4 A   | <b>4</b> B  | "      | 3    | "      |

| n ·         | 4  | "      | 5 A   | 5B          | 11     | 4    | **     |

| "           | 5  | **     | 6 A   | 6B          | "      | 5    | 11     |

| 11          | 6  | н      | 7A    | <b>7</b> B  | 11     | 6    | 11     |

| **          | 7  | 11     | 8 A   | 8B          | "      | 7    | 11     |

| n           | 8  | 11     | 9 A   | 9B          | Ħ      | 8    | 11     |

| n           | 9  | 11     | 10A   | 10B         | 11     | 9    | **     |

| "           | 10 | н      | 11A   | <b>1</b> 1B | n      | 10   | ••     |

| *1          | 11 | 99     | 12A   | 12B         | "      | 11   | 11     |

| 11          | 12 | **     | 13A   | 13B         | "      | 12   | •      |

| 11          | 13 | 91     | 14A   | 14B         | 11     | 13   | 11     |

| **          | 14 | **     | 15A   | 15B         | 11     | 14   | 11     |

| n           | 15 | ıı     | 16A   | 16B         | 11     | 15   | 11     |

| GROUND      |    | 17A    | 17B   | GRO         | UND    |      |        |

| GROU        | ND |        | 18A   | 18B         | GRO    | UND  |        |

U = UNIPOLAR

B = BIPOLAR

NOTE: TO CORRECTLY SET THE MODULES

INPUT RANGE ALL 9 DIP SWITCHES

MUST BE SET.

ADC- 1048

TOP TOGGLE SWITCH SET SCAN MODE, EITHER CONTINUOUS OR SINGLE 16 CHANNEL SCAN Princeton University Memo

TO: W. Rauch DATE: 4/16/87

FROM G. Kolinchak

P. Sichta

J. Wertenbaker

SUBJECT: ADC 320 Module

dropout problem investigation.

The cause of the NB Stepper Motor problem is beleived to be due to a 320 ADC module problem. The 320 occasionally misread a monitor value which caused the Stepper Motor Control Program to behave erratically.

It was found that out of 100 samples of a channel we would get 5 samples of another channels data. Looking at the "N" line in the crate and the "R12" line we find that the data for another channel may still be valid at "S1", or 400ns into the read cycle. This problem was caused by two areas in the write to memory circuit. A capacitor (C9) which set the duration of the write to memory pulse was 100pf. The schematic shows 68pf for its value. The pulse was 120ns in duration and the problem was aggravated by a delay which was caused by C8. (The C8 delay was 40ns.)

The proposed fix is to change C9 to 47pf which would then give a write memory pulse width of 55ns. The memory specification only requires a 25ns write pulse. Eliminating C8 would give us an additional 40ns safety margin. These changes would ensure a write memory to be completed at 330 ns into the CAMAC read. This leaves a good margin of  $\approx$ 70 before "S1"at 400ns.

Two modules have been modified and tested overnight without detecting any errors.

A plan to modify and replace 320 modules in the field should be investigated and implemented in the near future.

cc: N. Arnold

T. O'Conner

W. Bergin

N. Sauthoff

H. Feng

G. Schobert

- \_ \_ \_

- R. Gargiulo

- S. Hosein

- P. Hurst

- J. Kampershroer

- L. LAGIN

- J. McEnerney

- J. Montague

- G. Oliaro

SYSTEM

GOULD C.S.D. M

42.351 50 SHETS 5 SOUNE 42.352 100 SHETS 5 SOUNE 5.47.356 250 SHEETS 5 SOUNE Transiac

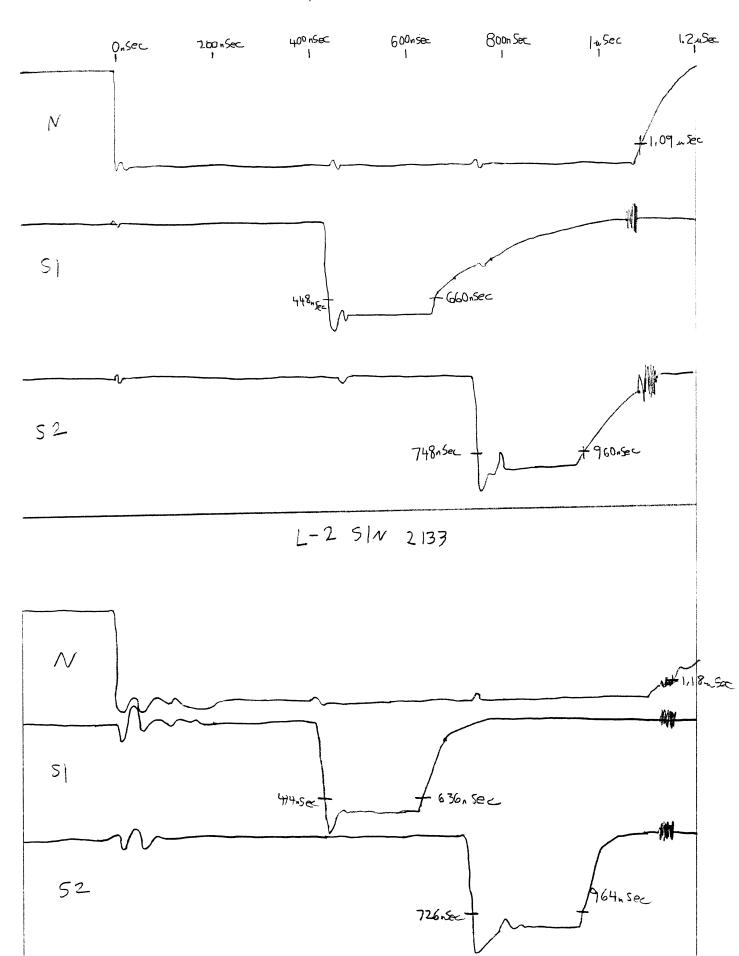

3952 Crate controller timing diagrams referencing 51,52, and the time The L-2 takes data to the leading edge of the "N" line in skt 10.

510+ 10 Bit 12

|       |             |             |        | ( lold, 4 new | )           |

|-------|-------------|-------------|--------|---------------|-------------|

| 5   N | Todator(ns) | S1 (n5)     | 52(15) | Generation    | model       |

| 1520  | 4 3 5       | 445         |        | 2             | 5003        |

| 2704  | 555         | 37 <i>5</i> |        | 4             | 5003        |

| 3087  | 550         | 365         | 680    | 4             | ZID         |

| 2849  | 555         | 365         |        | 4             | ZID         |

| 2134  | 390         | 415         |        | 3             | 218         |

| 0372  | 395         | 415         |        | 1             | Z14         |

| 2164  | 380         | 405         |        | 3             | 5003        |

| None  | 560         | 345         |        |               | Hsi's board |

| 2133  | 380         | 405         | 730    | 3             | Z1B         |

| 2530  | 545         | 365         |        | 4             | 5003        |

| 2210  | 380         | 395         |        | 3             | 5003        |

| 1809  | 410         | 435         |        | 2             | 5003        |

| 1690  | 420         | 440         |        | 2             | S003        |

| 1677  | 420         | 435         |        | 2             | \$003       |

| 2121  | 400         | 435         |        | 3             | not known   |

# 320 ADC MODULE YELLOW DOT MODIFICATION

John Wertenbaker 4/24/00

The following results were obtained with 0 volts on the channel 0 input and 8 volts (Hex C80) in all the other inputs. The module was given an F(0) A(0) command. Ideally, the module should read back 0 volts every time. But it was found that occasionally the module would read back data from another channel.

The data from the unmodified 320 module is subject to change until about 425 nSec after the N line goes active. This is acceptable for most L-2 crate controllers. But, it was found that some L-2 crate controllers clock the readback data later than other crate controllers.

The modification to the 320 module is as follows:

- 1) Remove C8.

- 2) Replace C9 with a 47pf capacitor.

- 3) Verify that C3 is 330pf.

- 4) Affix a yellow dot to the front panel of the module.

It is best to test the 320 module with L-2 crate controller S/N 2133. This L-2 clocks the data sooner than other L-2 crate controllers, making the problem show up more than others.